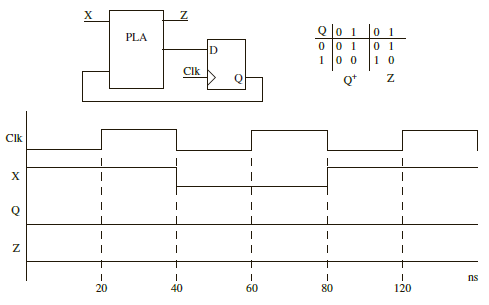

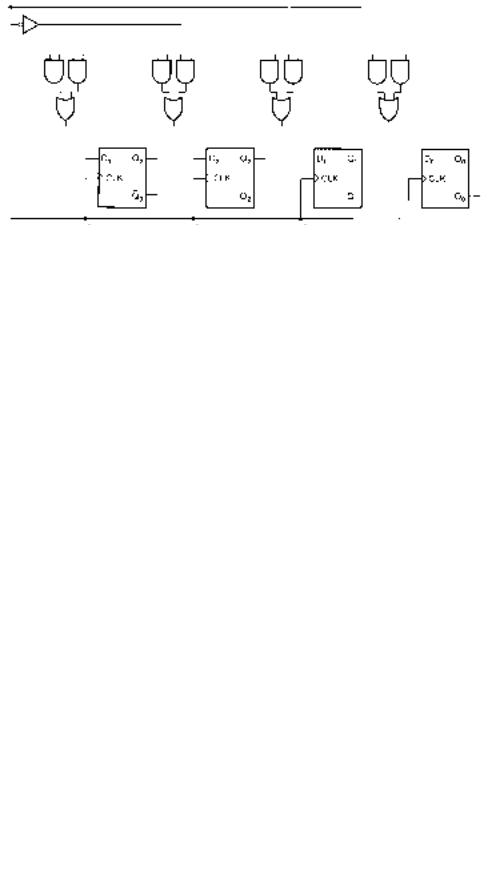

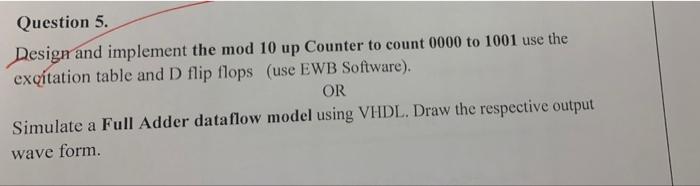

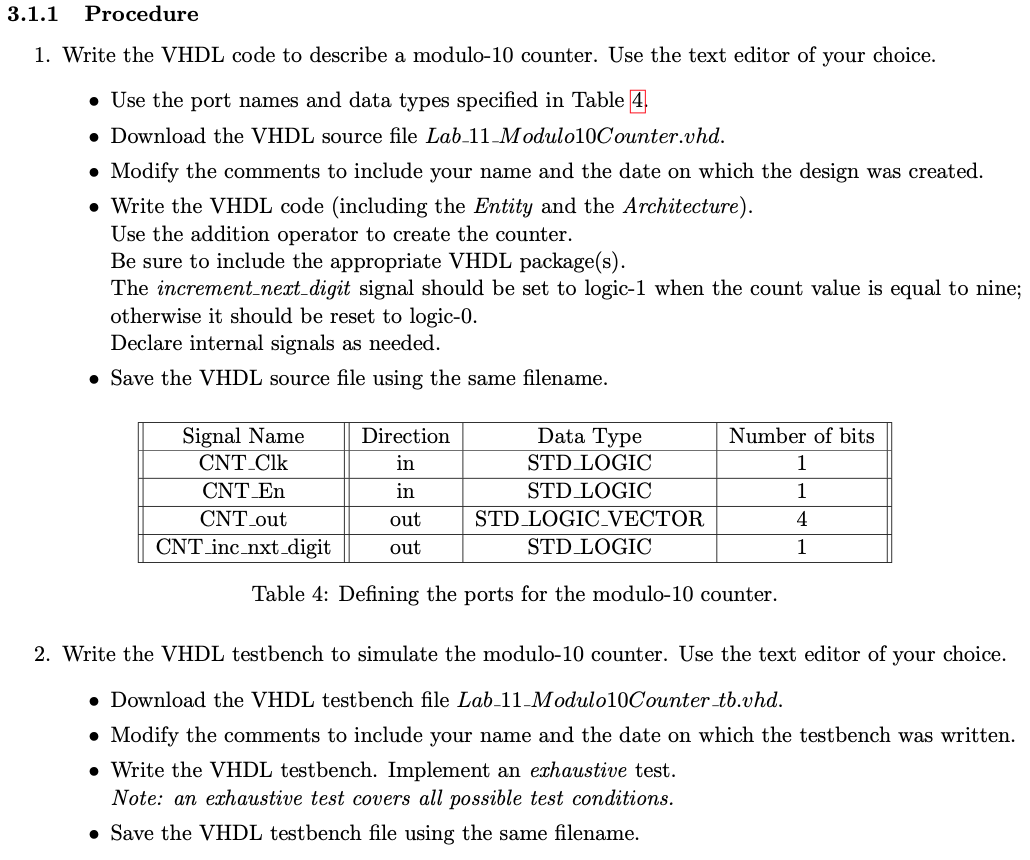

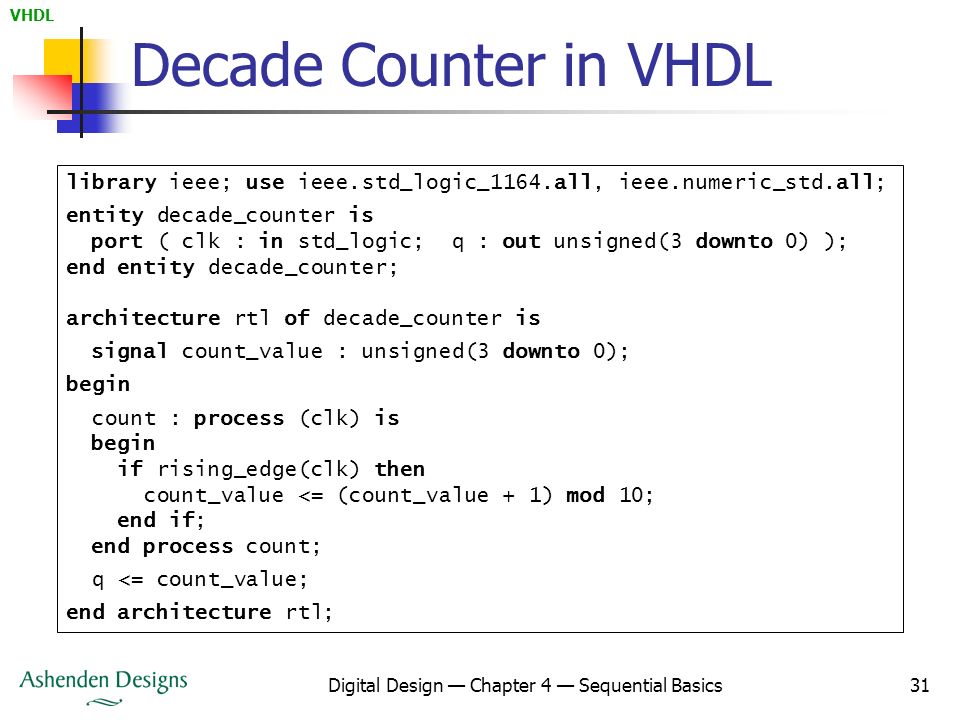

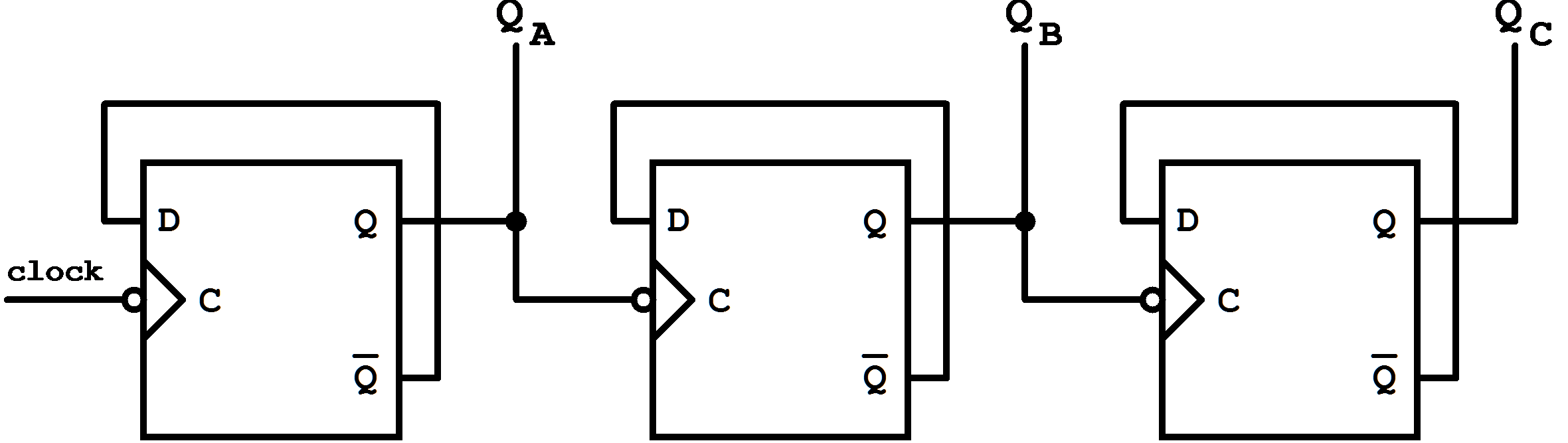

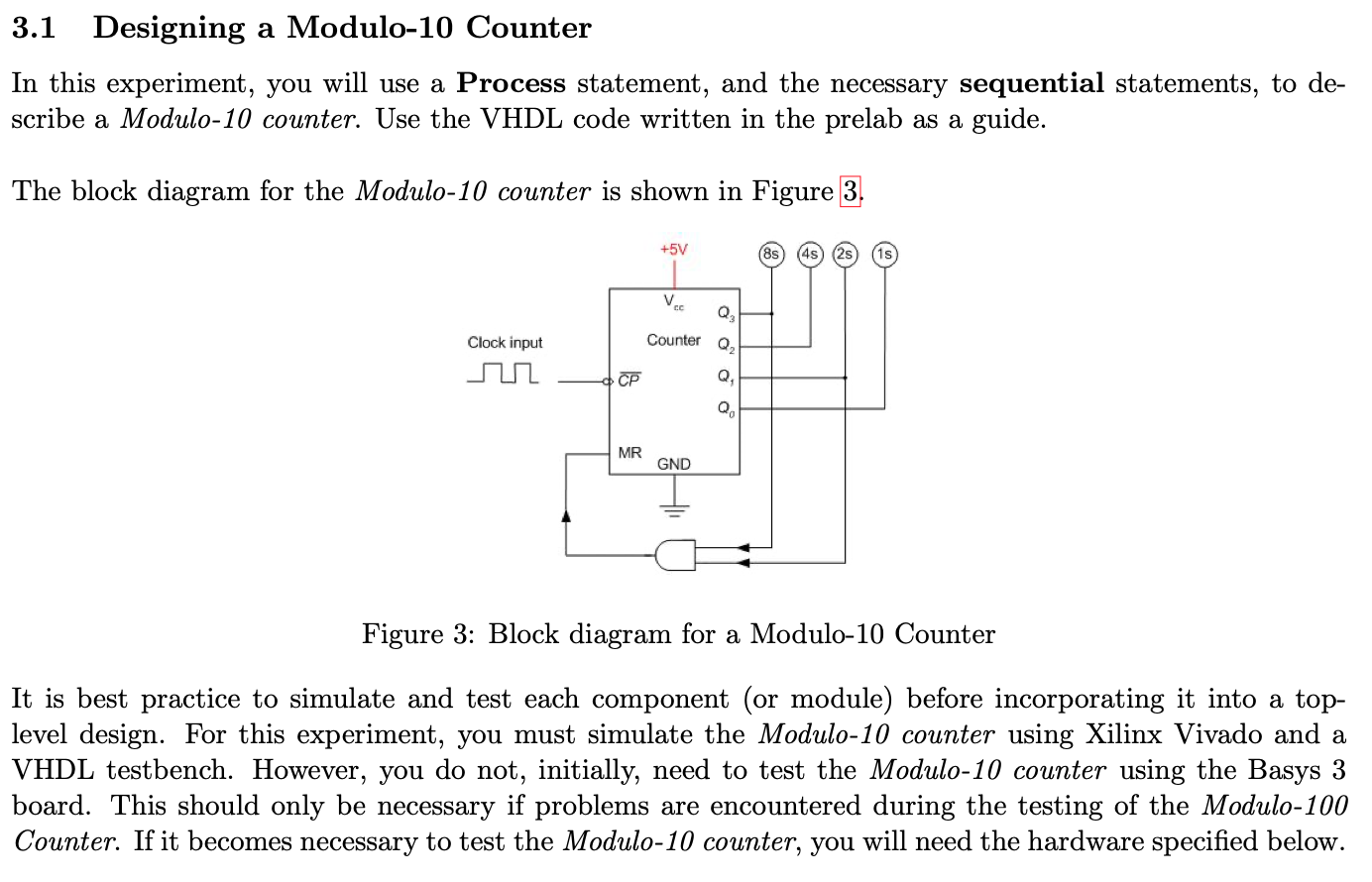

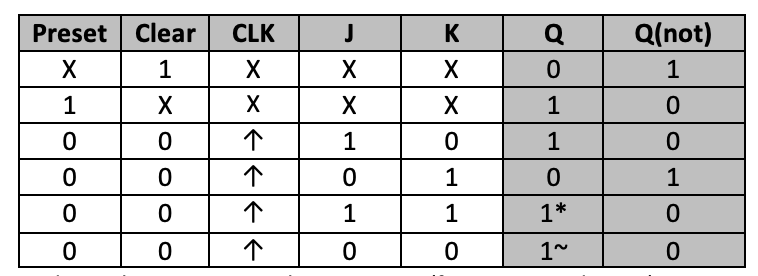

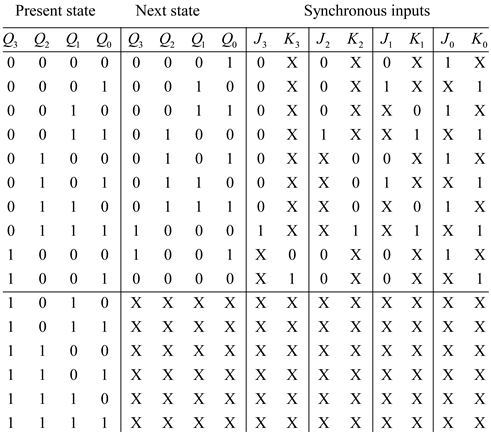

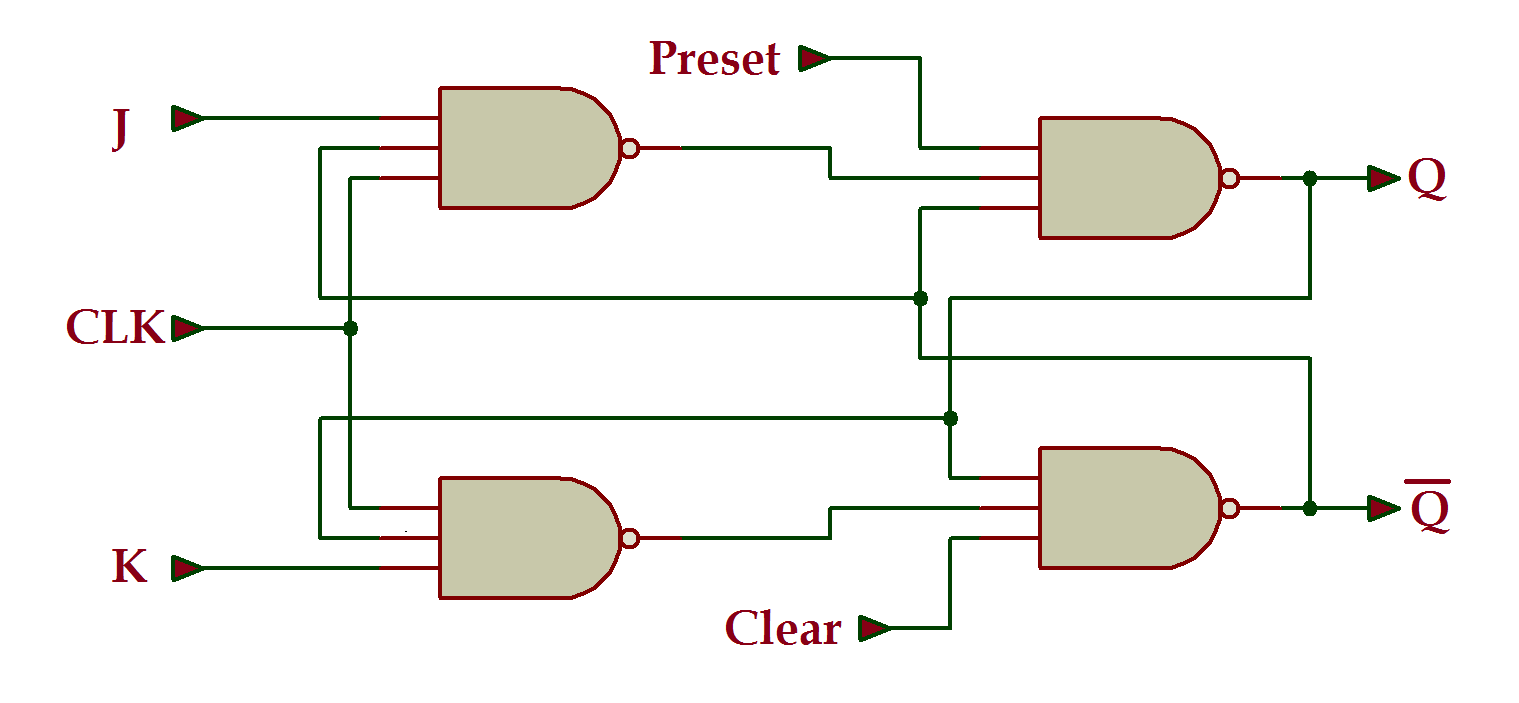

Design mod-10 synchronous counter using JK Flip Flops.Check for the lock out condition.If so,how the lock-out condition can be avoided? Draw the neat state diagram and circuit diagram with Flip Flops.

Design mod-10 synchronous counter using JK Flip Flops.Check for the lock out condition.If so,how the lock-out condition can be avoided? Draw the neat state diagram and circuit diagram with Flip Flops.

![PDF] Design and Implementation of Mod-6 Synchronous Counter Using Vhdl | Semantic Scholar PDF] Design and Implementation of Mod-6 Synchronous Counter Using Vhdl | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/bb7ae925b39e61478d0aab5df7d423a3e1f2be9b/5-Figure5-1.png)

![PDF] Design and Implementation of Mod-6 Synchronous Counter Using Vhdl | Semantic Scholar PDF] Design and Implementation of Mod-6 Synchronous Counter Using Vhdl | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/bb7ae925b39e61478d0aab5df7d423a3e1f2be9b/3-Figure2-1.png)